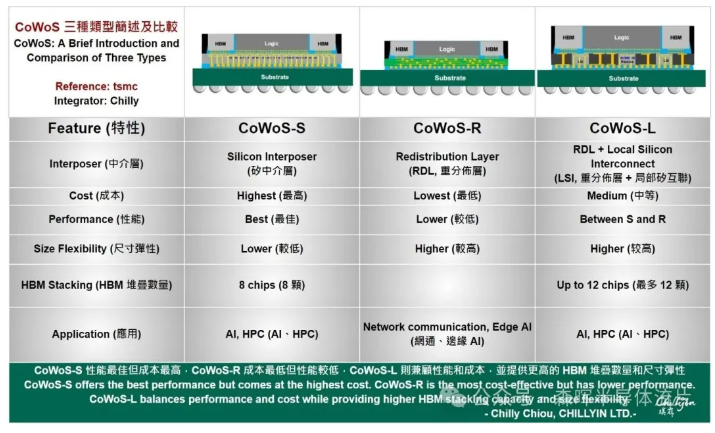

随着AI芯片与高性能计算(HPC)需求爆发,台积电CoWoS(Chip-on-Wafer-on-Substrate)封装技术成为行业焦点。其核心差异在于中介层(Interposer)的材料与结构设计,衍生出CoWoS-S、CoWoS-R、CoWoS-L三大技术路线。本文从性能、成本、应用维度解析三者差异。

1. CoWoS-S:硅中介层方案 —— 极致性能的代名词

技术特点:

硅通孔(TSV)技术:通过高密度硅基互连实现超低延迟,散热效率领先,适配算力密集型场景。

旗舰芯片标配:NVIDIA Hopper H100/H200、AMD MI300等AI训练芯片均采用此方案,满足千亿级参数模型的数据吞吐需求。

核心挑战:

成本与良率瓶颈:硅材料脆性导致大尺寸晶圆(>2000mm²)良率不足50%,单片封装成本超万元。

应用局限:主要服务于超算中心、云端AI服务器等高性能刚需领域。

2. CoWoS-R:RDL中介层方案 —— 性价比与灵活性的平衡者

创新设计:

聚合物基重布线层:采用铜导线与有机介质堆叠,支持更自由的封装尺寸扩展,降低30%-40%制造成本。

适应性升级:抗形变能力优于硅基方案,适用于边缘AI设备、5G基站模块等对温差敏感的场景。

性能妥协:

带宽限制:互连密度仅为CoWoS-S的1/3,难以支撑多HBM(高带宽内存)堆叠需求。

典型应用:博通交换芯片、华为昇腾边缘推理卡等中低算力硬件。

3. CoWoS-L:混合架构方案 —— 破局HBM堆叠难题

技术融合突破:

LSI局部硅互连+RDL全局布线:在关键信号路径(如CPU-GPU通道)嵌入微型硅中介层,其余区域采用RDL降低成本,实现每瓦性能比优化20%。

HBM堆叠革命:最多支持12颗HBM3e芯片集成,显存容量可达CoWoS-S方案的1.5倍,Blackwell B200/GB200系列借此实现单卡120TB/s带宽。

商业价值:

车企智驾芯片优选:特斯拉Dojo 2.0、蔚来ADAM 2.0等下一代平台计划导入该方案,兼顾能效与扩展性需求。

技术选型决策矩阵

| 维度 | CoWoS-S | CoWoS-R | CoWoS-L |

|---|---|---|---|

| 性能优先级 | ★★★★★ | ★★★☆☆ | ★★★★☆ |

| 成本控制 | ★★☆☆☆ | ★★★★☆ | ★★★☆☆ |

| HBM扩展性 | 8颗 | ≤4颗 | 12颗 |

| 典型客户 | NVIDIA/AMD云端芯 | 博通/高通通信芯 | 车企/边缘AI芯片 |

行业趋势前瞻

材料创新:东芝开发氮化硅中介层原型,导热系数提升2倍,或成下一代低成本方案。

国产替代:长电科技XDFOI方案已实现CoWoS-L类封装量产,客户导入华为海思、地平线等企业。

CoWoS技术分化本质是性能、成本、可靠性的“不可能三角”权衡。未来,随着Chiplet生态成熟与3D堆叠技术突破,中介层设计将持续重构算力芯片的竞争格局。

更多关于砷化镓流片、碳化硅流片、氮化镓流片、4寸晶圆流片、6寸晶圆流片、8寸晶圆流片、12寸晶圆流片等业务,可联系15262626897详细沟通。